一、实验目的

1. 认识全加器的意义和应用;

2. 了解多位全加器的串行进位和并行进位的意义;

3. 熟悉4位全加器(74LS183)的逻辑功能及使用。

二、实验器材

1. VCC

2. Ground

3. 双1位全加器74LS183

4. 指示灯

5. 四输入七段数码管

三、实验原理

加法器是产生数的和的装置。加数和被加数为输入,和数与进位为输出的装置为半加器。以单位元的加法器来说,有两种基本的类型:半加器和全加器。

1. 半加器

半加器有两个输入和两个输出,输入可以标识为A、B或X、Y,输出通常标识为和S和进位CO。A和B经“或”运算后,即为和S,经“与”运算后即为进位CO。其逻辑表达式为:

S=A'B+AB'=A?B;CO=AB

半加器虽能产生进制值,但半加器本身并不能处理进制值。半加器真值表如1,电路图如图1。

表1 半加器真值表

输 入 | 输 出 | ||

A | B | S | CO |

0 | 0 | 0 | 0 |

0 | 1 | 1 | 0 |

1 | 0 | 1 | 0 |

1 | 1 | 1 | 1 |

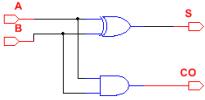

图1 半加器电路图

2. 全加器

在将两个多位二进制数相加时,除了最低位以外,每一位都应该考虑来自低位的进位,即将对应的位数和来自低位的进位3个数相加。这种运算称为全加,所使用的电路称为全加器。全加器引入了进制值的输入,以计算较大的数。为区分全加器的两个进制线,在输入端的记作CI,在输出端的则记作CO。其逻辑表达式为:

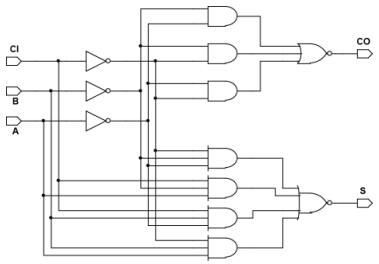

全加器三个二进制的输入,其中一个是进制值的输入,所以全加器可以处理进制值。全加器可以用两个半加器组合而成。真值表如表2,全加器电路图如图2。

表2 全加器真值表

输 入 | 输 出 | |||

CI | A | B | S | CO |

0 | 0 | 0 | 0 | 0 |

0 | 0 | 1 | 1 | 0 |

0 | 1 | 0 | 1 | 0 |

0 | 1 | 1 | 0 | 1 |

1 | 0 | 0 | 1 | 0 |

1 | 0 | 1 | 0 | 1 |

1 | 1 | 0 | 0 | 1 |

1 | 1 | 1 | 1 | 1 |

图2 全加器电路图

四、设计要求

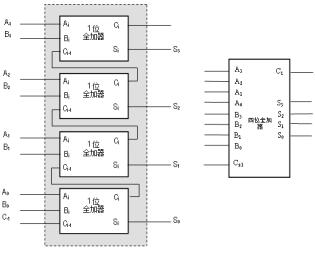

由两片74LS183构成串行进位4位全加器,如图3所示。验证4位全加器的逻辑功能。要求将输入及输出连接数码管,并记录数码管的显示码。

图3 串行进位4位全加器