实验

中规模组合逻辑电路实验3:译码器及其应用

学时

1

实验介绍

实验指南

实验资料

实验台

一、实验目的

1. 认识译码器的定义、功能及基本使用;

2. 熟悉译码器(74HC138)的功能和级联。

二、实验器材

1. VCC

2. Ground

3. 3线-8线反相译码器74HC138

4. 指示灯

三、实验内容

利用两片3线-8线译码器74HC138组成4线-16线译码器,要求:将输入的4位二进制代码D3D2D1D0译成16个独立的低电平信号Z0'~Z15'。

四、实验原理

1. 译码器

译码器(Decoder)的逻辑功能是将每个输入的二进制代码译成对应的输出高、低电平信号或另外一个代码。因此,译码是编码的反操作。常用的译码器电路有二进制译码器、二-十进制译码器和显示译码器三类。

2. 74HC138

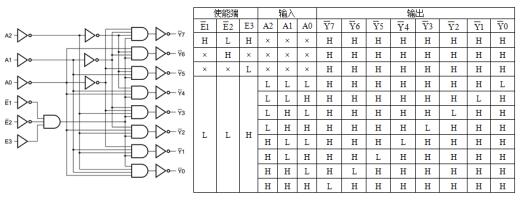

74HC138是用CMOS门电路组成的3线-8线译码器,该译码器可接受3位二进制加权地址输入(A0,A1和A2),并当使能时,提供8个互斥的低有效输出(Y0'~Y7')。74HC138特有3个使能输入端:两个低有效(E1'和E2')和一个高有效(E3)。除非E1'和E2'置低且E3置高,否则74HC138将保持所有输出为高。74HC138逻辑图及真值表信息如图1所示。

图1 74HC138逻辑图及真值表

根据74HC138真值表得出,当E1'和E2'置低且E3置高时,输入和输出之间的逻辑函数式为:Y0'=(A2'A1'A0')',Y1'=(A2'A1'A0)',Y2'=(A2'A1A0')',Y3'=(A2'A1A0)',Y4'=(A2A1'A0')',Y5'=(A2A1'A0)',Y6'=(A2A1A0')',Y7'=(A2A1A0)'。

您还没有登录,请先登录

您还没有登录,请先登录

您还没有登录,请先登录