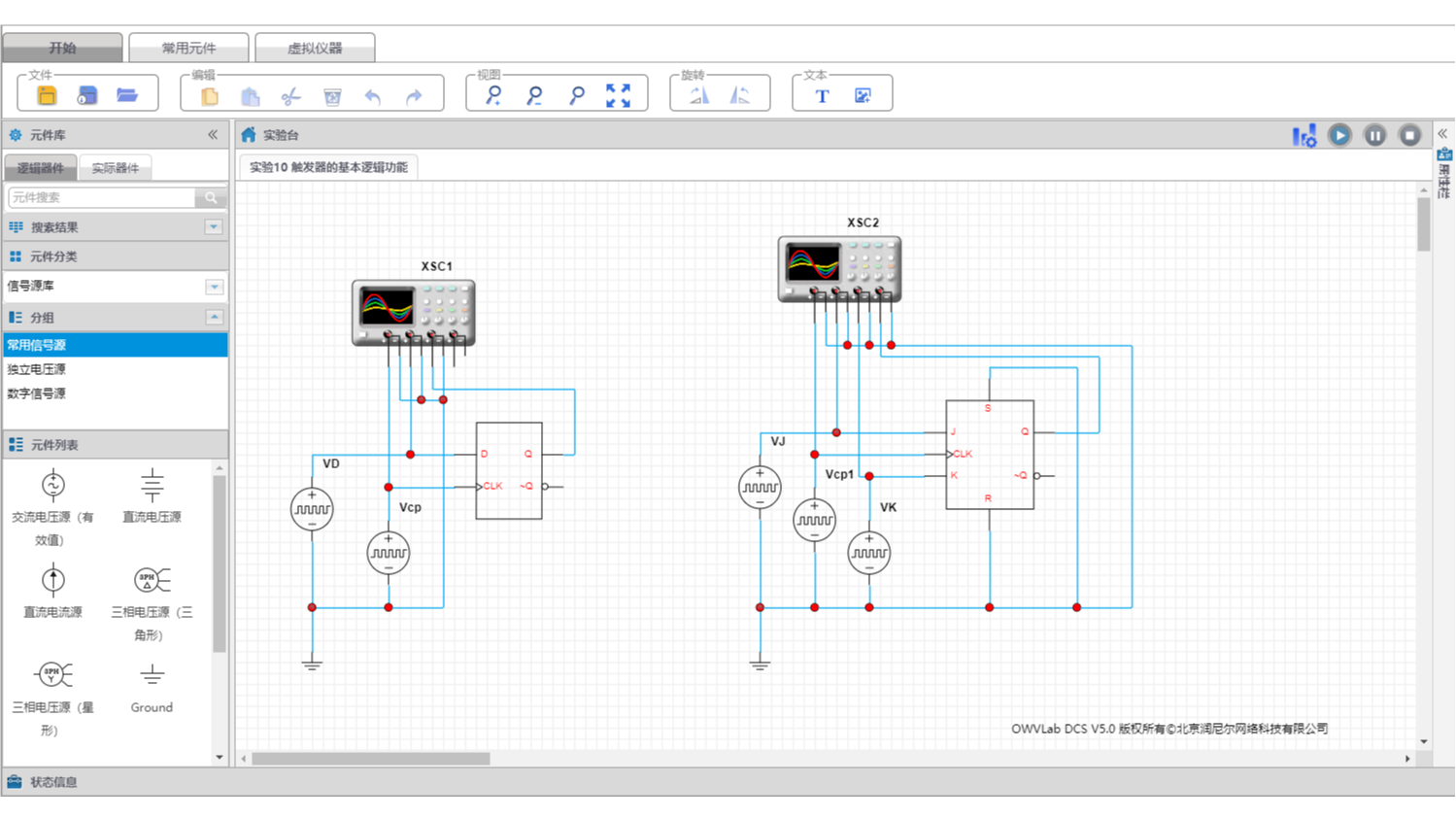

一、实验目的

1. 认识D触发器和JK触发器的基本功能;

2. 熟悉触发器的输入、输出信号及时钟的波形关系。

二、实验器材

1. Ground

2. 脉冲电压源

3. 上升沿触发D触发器

4. 上升沿触发JK触发器

5. 四通道示波器

三、实验原理

触发器是指能够存储1位二值信号的基本单元电路。其能够具有两个稳定状态,就说电路存在记忆功能,两个稳定状态分别定义为置位(set)和复位(reset),在置位状态时,触发器记忆二进制数1,在复位状态时,触发器记忆二进制数0。

按电路结构形式,触发方式分为电平触发、脉冲触发和边沿触发三种。根据触发逻辑功能的不同分为SR触发器、JK触发器、T触发器、D触发器等几种类型。

电平触发器在CP=1时有效,当CP=1的时间过长时,可能有不稳定情况出现,为克服这种错误现象,就设计了边沿处触发器。边沿触发器(Edge-triggered FF)是一种脉冲型触发器,因为其输入和输出的变化只在控制信号CP脉冲的边沿发生,即CP的上升沿或下降沿,所以有上升沿触发的边沿触发器和下降沿触发的边沿触发器两种。因为边沿触发器的状态只可能在CP的跳变沿才会发生改变,所以触发器的稳定性大大提高。

1. 边沿D触发器

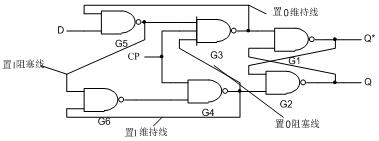

上升沿触发的D触发器(Positive-edge-triggered DFF),又称为维持阻塞触发器,因为在电路上有称为维持线和阻塞线的连线,他们保证信号在边沿的作用,如图1所示,其工作原理如下。

图1 边沿D触发器及其符号

当CP=0时,G3、G4输出为1,G1、G2输出保持不变。G5输出为D,G6输出D'。

设D=0,CP从0到1时,G3输出从1到0,反馈线封锁了输入,维持输出为0,而G4输出不变,则Q=0,Q'=1。如果CP为1后,D发生变化,由于有置1阻塞线,也不会改变输出了,置0维持线保证输出为0。

设D=1,CP从0到1时,G3输出为1不变,而G4输出从1到0+,反馈线封锁G3和G6,维持G4为0,则Q=1,Q'=0。如果CP为1后,D发生变化,由于有置0阻塞线,也不会改变输出了,置1维持线保证输出为1。

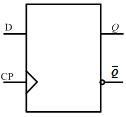

上升沿D触发器的特性方程为:

Q*=[D]·CP↑

功能表如表1所示。

表1 上升沿D触发器功能表

CP | D | Q* |

↑ | L | L |

↑ | H | H |

2. 边沿JK触发器

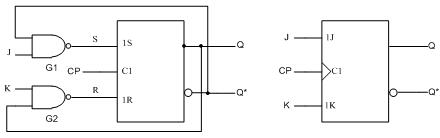

JK触发器也是从RS触发器改进而得到的,如图2所示。上升沿触发的JK触发器(Positive -edge-triggered JK FF),又称为利用传输迟延的边沿触发器,它是利用门电路的传输时间的不同来实现边沿触发的,虽然工作原理不同,但是实际的交过是一样的,都在时钟的边沿输入、输出。

图2 JK触发器及其符号

上升沿JK触发器特性方程为:

Q*=[JQ'+K'Q]·CP↑

功能表如表2所示。

表2 JK触发器特性表

CP | J | K | Q | Q* |

↑ | L | L | L | L |

↑ | L | L | H | H |

↑ | L | H | L | L |

↑ | L | H | H | L |

↑ | H | L | L | H |

↑ | H | L | H | H |

↑ | H | H | L | H |

↑ | H | H | H | L |