实验

异步十进制计数器的设计

学时

1

实验介绍

实验指南

实验资料

实验台

一、实验目的

1. 认识异步计数器的结构特点;

2. 了解基于JK触发器设计异步十进制计数器的方法过程。

二、实验器材

1. VCC

2. Ground

3. 上升沿触发JK触发器

4. 2输入与门

5. 脉冲电压源

6. 四输入七段数码管

7. 八通道示波器

三、实验原理

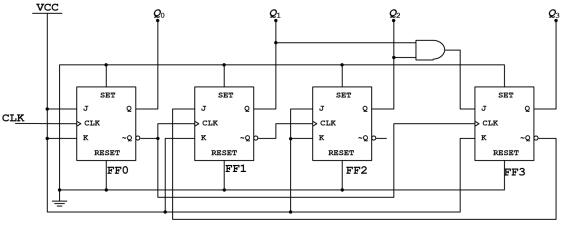

异步十进制加法计数器将4位二进制计数器在计数过程中跳过从1010到1111这6个状态而得到。图1为异步十进制计数器的电路。

图1 异步十进制计数器电路

如果计数器从Q3Q2Q1Q0=0000开始计数,由图可知在输入第8个计数脉冲以前FF0、FF1和FF2的J和K始终为1。在此期间虽然Q0输出的脉冲也送给了FF3,但由于每次Q0的上升沿到达J=Q2Q1=0,所以FF3一直保持0状态不变。

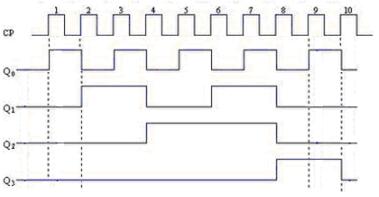

当第8个计数脉冲输入时,由于J3=K3=0,所以Q0的上升沿达到以后FF3由0变为1。 同时,J1也随Q3'变为0状态。第9个计数脉冲输入以后,电路状态变成Q3Q2Q1Q0=1001。第10个计数脉冲输入后,FF0翻转成0,同时Q0的上升沿使FF3置0,于是电路从1001返回到0000,跳过了1010-1111这6个状态,成为十进制计数器。图2为电路的时序图。

图2 电路的时序图

您还没有登录,请先登录

您还没有登录,请先登录

您还没有登录,请先登录