实验

可控计数器电路设计

学时

1

实验介绍

实验指南

实验资料

实验台

一、 实验目的

1. 掌握D触发器的应用;

2. 掌握时序逻辑电路的设计方法;

3. 熟悉可控计数器的实现方法。

二、 实验器材

1. 2输入与门

2. 2输入或非门

3. 非门

4. 上升沿触发D触发器

5. 数字时钟信号源

6. 数字常量

7. 四输入七段数码管

8. Ground

三、 设计要求

用D触发器设计一个可控计数器。当X=0时,计数顺序为4→5→1→3→2→6→4;X=1时,计数顺序为4→6→2→3→1→5→4。组合电路采用与门、或非门及非门实现。

四、 设计流程

1. 逻辑抽象,得到电路的状态转移图

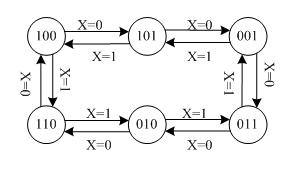

根据设计要求作出状态转移图,如图1所示。

图1 可控计数器状态转移图

2. 可控计数器的状态转移表

由可控计数器的状态转移图可知,计数共有6个状态,因此采用3个触发器,其状态转移表如表1所示。

表1 可控计数器状态转换表

X | PS | NS | ||||

Q2n | Q1n | Q0n | Q2n+1 | Q1n+1 | Q0n+1 | |

0 | 1 | 0 | 0 | 1 | 0 | 1 |

0 | 1 | 0 | 1 | 0 | 0 | 1 |

0 | 0 | 0 | 1 | 0 | 1 | 1 |

0 | 0 | 1 | 1 | 0 | 1 | 0 |

0 | 0 | 1 | 0 | 1 | 1 | 0 |

0 | 1 | 1 | 0 | 1 | 0 | 0 |

1 | 1 | 0 | 0 | 1 | 1 | 0 |

1 | 1 | 1 | 0 | 0 | 1 | 0 |

1 | 0 | 1 | 0 | 0 | 1 | 1 |

1 | 0 | 1 | 1 | 0 | 0 | 1 |

1 | 0 | 0 | 1 | 1 | 0 | 1 |

1 | 1 | 0 | 1 | 1 | 0 | 0 |

3. 确定表达式

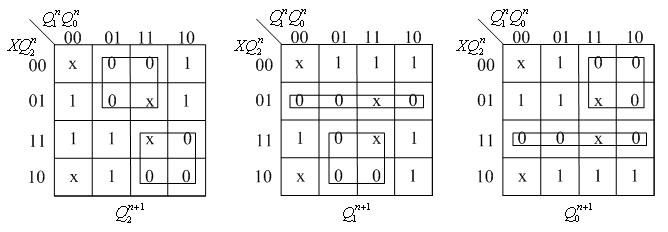

根据表1得到Q2n+1、Q1n+1、Q0n+1的状态卡诺图,如图2所示,并由卡诺图得出状态方程,如式(1)所示。

图2 可控计数器状态卡诺图

4. 表达式化简

根据式(1)以及D触发器的特性方程Qn+1=D,化简得到该电路的状态方程和激励方程,如式(2)所示。

5. 确定逻辑电路图

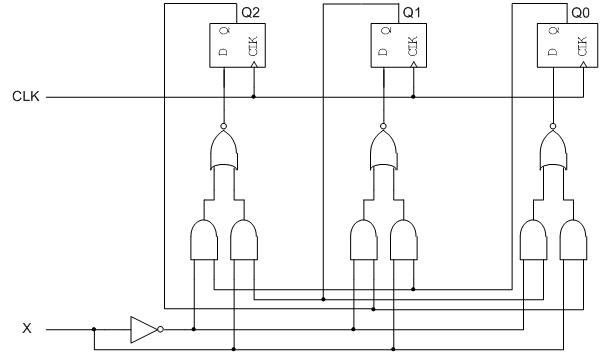

根据式(2),采用D触发器、与门、或非门以及非门方式得到可控计数器的电路原理图,如图3所示:

图3 基于D触发器的可控计数器原理图

您还没有登录,请先登录

您还没有登录,请先登录

您还没有登录,请先登录